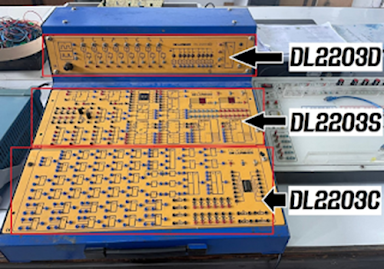

2. Alat dan bahan[Kembali]

Kelebihan JK Flip-flop adalah tidak adanya kondisi terlarang atau yang berarti di beri berapapun inputan asalkan terdapat clock maka akan terjadi perubahan pada keluarannya / outputnya. berikut adalah symbol dan tabel kebenaran dari JK Flip-Flop.

3. Rangkaian Simulasi[Kembali]

4. Prinsip Kerja[Kembali]

prinsip kerja rangkaian diatas adalah disini menggunakan 4 buah jk flipflop yang yang jk nya telah terhubung dengan power. sehingga input pada jk flipflopnya bersifat toggle. maka Output toogle pada masing-masing IC akan berubah sesuai aktif pada clock yaitu aktif low (Fall time).

pada percobaan pertama clock inputnya hanya terdapat pada jk flipflop pertama atau pada paling kanan saja sehingga saat clock yang mula mula dari 0 menuju rise time. maka output jk flipflop yang pertama tidak ada perubahan begitu juga pada jk stereusnya.

kemudian saat clock tersebut dalam keadaan faal time maka jk flipflop pertama akan berubah menjadi 1. namun jk flipflop kedua tidak berpengaruh karena jk flipflop kedua bergantung pada output di jk flipflop pertama sehingga terjadi delay time. sehinnga clock ic kedua dalam keadaan rise time sehingga output ic kedua berlogika 0 begitun seterusnya sampai ic ketiga dan keempat mendapat kenaikan atau penurunan dari flipflop

1. Analisa output percobaan berdasarkan ic yang digunakan

Jawab:

Berdasarkan percobaan yang dilakukan ic yang digunakan adalah 74LS112 yang merupakan sebuah JK flipflop. pada JK flipflop ini memiliki Inputan berupaa set (s), reset (R), J, K dan clok dan outputannya yaitu Q dan Q'. pada rangkan Percobaan Inputan R dan s dihubung secara keseluruhan pada saklar sw- spdt yang telah terhubung dengan power dan ground kemudian inputan JK flipflop dihubungkan pada Power Inputnya clock pada JK flipflop I dihubungkan dengan clock sedangkan 3 JK flipflop lainnya mendapat input dari Q JK flipflop sebelumnya setiap JK flipflop ini dipasang logic probe sebagai pencacah aner 4 Git counter.

Pada rangkain percobaan ini outputan dan lc JK flipflop berupa toogle. clock tersebut hanya di inputan pada JK flipflop Pertama yang dimana inputan clocknya aktiflow yaitu pada kondisi fall time maka outputan dari JK flipflop yg berupa toggle kendalikan oleh kondisi fall time pada masing maging clock.

pada percobaan 1, clock yang mula-mula dan nol ke rise time maka output JK flipflop yang pertama tidak mengalami Perubahan (tetap nol). begitun pun JK flipflop kedua Sampai Keempat (tetap nol), maka output percobaan awal dari nol

clock dalam fall time maka JK flipflop yang paling ujung atau yang pertama akan naik ke 1. pada JK flipflop yang kedua tidak berpengaruh karena la bergantung terhadap Q pada JK flipflop pertama. Sehingga lc kedua ini dalam keadaan rise time sehingga output Ic kedua berlogika nol. begitupun seterusnya sampai lc ke-4

Berdasarkan percobaan dan timing diagram yang telah dibuat di dapatkan perubahan output secara berkala. dimana terdapat delay diseiap perubahan outputnya kama ic ke-2 sampai ke 4 Inputnya saling bergantung terhadap Ic sebelumnya. Sehingga Pada percobaan 1 ini diperoleh kenaikan tersebut dari 0000, ooo1, hingga sampai 1111. kenaikan perhitungan ini disebut counter up karena terdapat kenaikan dari nol sampai 15. atau 0-15.

2 .Analisa sinyal output yang dikeluarkan JK FlipFlop kedua dan ketiga!

Jawab:

Dari rangkain yang dicobakan JK FlipFlop ke 2 sampai ke 4 bergantung pada setiap JK FlipFlop sebelumnya. maksudnya keluaran sinyal dari JK FlipFlop kedua sampai keempat tersebut didapatkan dari output JK FlipFlop sebelumnya.

Output JK FlipFlop kedua diperoleh saat input JK FlipFlop kedua ini mendapatkan Input dari Q output dari JK FlipFlop. Pertama karna clocknya berupa aktif low dan delay time Perubahan output JK FlipFlop kedua sampai ke 4 adalah kelipatan fall time clock dari JK FlipFlop sebelumnya. Berdasarkan ini sinyal output kedua akan berubah ketika mendapatkan inputan dari output Q pada JK FlipFlop. Sehingga didapatkan delay time pada JK FlipFlop ke-2 Ini-outputnya dan kelipatan fall time dari clock pertama, Yaitu fall time clock kedua (kelipatan 1).

Pada JK FlipFlop ketiga sinyal outputnya akan berubah saat Input clock JK FlipFlop mendapat input dari JK FlipFlop kedua dengan output . maka juga terdapat delay time pada keluaran Sinyal JK FlipFlop ketiga yang dimana outputnya, akan berubah dari kelipatan fall time clock kedua yaitu diperoleh fall time clock keempat (4) (kelipatan 2), maka antara sinyal output jk flipflop 2 dan 3 terjadi bergilir.

HTML klik disini

Rangkaian klik dsini

Video klik disini

.png)