1.Tujuan[kembali]

- Untuk menyelesaikan tugas elektronika yg diberi oleh bapak Darwison,M.t

- untuk memahami materi sub-chapter 5.2

- Menyelesaikan masalah yang berhubungan dengan materi sub-chapter 5.2

2.Alat dan Bahan[kembali]

battery

|

| Baterai atau elemen kering adalah salah satu alat listrik yang berfungsi sebagai penyimpan energi listrik dan mengeluarkan tegangan dalam bentuk listrik (sebagai sumber tegangan)Terdapat dua jenis baterai yaitu : 1. Baterai Primer Baterai adalah baterai yang hanya dapat digunakan sekali, menggunakan reaksi kimia yang tidak dapat dibalik (irreversible reaction). pada umumnya dijual adalah baterai yang bertegangan listrik 1,5 volt. 2. Baterai Sekunder Baterai sekunder atau biasanya disebut rechargeable battery adalah baterai yang dapat di isi ulang menggunakan reaksi kimia yang bersifat dapat dibalik (reversible reaction) biasanya digunakan pada telepon genggam. Adapun salah satu persamaan menghitung tegangan adalah : P = V x I Keterangan : P = Daya (W) V = Tegangan yang terukur (V) I = Arus yang terukur (I) |

2.transistor

Transistor adalah alat semikonduktor yang dipakai sebagai penguat, sebagai sirkuit pemutus dan penyambung arus (switching), stabilisasi tegangan, dan modulasi sinyal. Transistor dapat berfungsi semacam kran listrik, di mana berdasarkan arus inputnya (BJT) atau tegangan inputnya (FET), memungkinkan pengaliran listrik yang sangat akurat dari sirkuit sumber listriknya.

3.Dasar teori[kembali]

JFET adalah perangkat tiga terminal dengan satu terminal yang mampu mengendalikan arus antara dua lainnya. . UntukJFET transistor, perangkat saluran-n akan muncul sebagai perangkat yang menonjol . Konstruksi dasar JFET n-channel ditunjukkan pada Gambar 5.2.

|

| gambar 5.9 |

tegangan negatif 1 V telah diterapkan antara gerbang dan terminal sumber untuk level VDS rendah. Efek dari VGS bias negatif yang diterapkan adalah untuk menetapkan daerah penipisan yang serupa dengan yang diperoleh dengan VGS 0 V tetapi pada tingkat VDS yang lebih rendah. Oleh karena itu, hasil dari penerapan bias negatif pada gate adalah untuk mencapai tingkat saturasi pada tingkat yang lebih rendah dari VDS

Resistor Terkendali Tegangan

Persamaan berikut akan memberikan perkiraan pertama yang baik ke level resistansi dalam hal tegangan yang diberikan

dimana ro adalah resistansi dengan VGS = 0 V dan rd resistansi pada level tertentu

dari VGS.

Untuk JFET n-channel dengan ro sama dengan 10 kohm (VGS= 0 V, VP=- 6 V),

akan menghasilkan 40 k pada VGS 3 V.

|

| pembalikan bahan jenis-p dan n |

kesimpulan

- Arus maksimum didefinisikan sebagai IDSS dan terjadi ketika VGS= 0 V dan VDS >| VP | seperti yang ditunjukkan pada Gambar 5.14a.

- Untuk tegangan gerbang-ke-sumber, VGS kurang dari (lebih negatif dari) pinch-offtingkat, arus drain adalah 0 A (ID 0 A) seperti yang terlihat pada Gambar. 5.14b.

- Untuk semua level VGS antara 0 V dan level pinch-off, ID saat ini akankisaran antara IDSS dan 0 A, masing-masing, seperti yang ditinjau oleh Gambar. 5.14c.

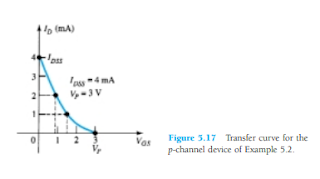

1. Buatlah sketsa kurva transfer untuk perangkat p-channel dengan IDSS 4 mA dan VP 3 V.

Jawab :

Pada VGS=VP/2 = 3 V/2 = 1.5 V, ID = IDSS/4 = 4 mA/4 = 1 mA. At ID = IDSS/2 = 4 mA/2 = 2 mA, VGS = 0.3VP = 0.3(3 V) 0.9 V Kedua titik plot muncul pada gambar 5.17 bersama poin-poin yang ditentukan oleh Idss dan Vp.

2. Buatlah sketsa kurva transfer yang ditentukan oleh Idss 12 mA dan Vp 6 Volt

Jawab :

Dua titik plot ditentukan oleh

IDSS =12 mA and VGS = 0 V

ID = 0 mA and VGS=VP

Pada Vgs = Vp/2 = -6 V/2 = -3 V arus drain akan ditentukan oleh ID=Idss/4 = 12 mA/4 = 3 mA. Pada IDSS/2 = 12 mA/2 = 6 mA gerbang ke sumber tegangan ditentukan oleh Vgs = 0,3 Vp = 0,3 (-6 V) = -1,8 V. Keempat titik plot didefenisikan dengan baik pada Gambar 5.16 dengan kurva transfer lengkap.

Untuk perangkat p-channel persamaan Shockley (5.3) masih dapat diterapkan persis seperti itu

muncul. Dalam hal ini, baik VP maupun VGS akan bernilai positif dan kurva akan menjadi cermin

gambar kurva transfer diperoleh dengan n-channel dan nilai batas yang sama.

3.2 problem [kembali]

1. Apa perbedaan utama antara karakteristik kolektor transistor BJT dan transistor

menguras karakteristik transistor JFET? Bandingkan satuan dari setiap sumbu dan pengontrolnya

variabel. Bagaimana reaksi IC terhadap peningkatan level IB versus perubahan ID terhadap nilai VGS yang semakin negatif? Bagaimana jarak antar langkah IB dibandingkan dengan jarak antar langkah

langkah-langkah VGS? Bandingkan VCsat dengan VP dalam menentukan daerah nonlinier pada tingkat tegangan keluaran yang rendah

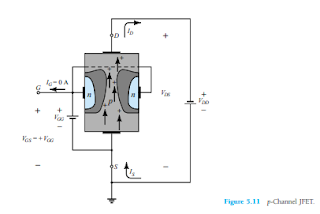

2. Secara umum, berikan pendapatmu tentang polaritas berbagai tegangan dan arah arus untuk an

JFET n-channel versus JFET p-channel.

3.3 pilihan ganda[kembali]

1. Bagian atas saluran tipe-n dihubungkan melalui kontak ohmik ke terminal yang disebut dengan ....

a. Drain

b. Source

c. Basis

d. Kolektor

Jawab : A

Bagian atas saluran tipe-n dihubungkan melalui kontak ohmik ke terminal yang disebut drain (D)

2. Perbedaan yang paling utama antara Transistor Bipolar (NPN/PNP) dengan FET adalah dalam pengendaliannya yaitu ....

a. Bipolar menggunakan tegangan (V), sedangkan FET menggunakan arus (I)

b. Bipolar menggunakan daya (P), sedangkan FET menggunakan arus (I)

c. Bipolar menggunakan arus (I), sedangkan FET menggunakan tegangan (V)

d. Bipolar menggunakan daya (), sedangkan FET menggunakan tegangan (V)

Jawab : C

Perbedaan yang paling utama antara Transistor Bipolar dan FET adalah pada pengendalian arus dan tegangannya, pada Bipolar menggunakan arus (I) sedangkan pada FET menggunakan tegangan (V).

4.Percobaan[kembali]

1,prosedur percobaan

- Siapkan alat dan bahan yang dibutuhkan dalam membuat rangkaian tersebut.

- alat dan bahan yang digunakan adalah baterai, ground,transistor JFET (2N3819)

- Rangkailah alat dan bahan tersebut seperti gambar di bawah ini.

- Simulasikan pada software proteus

2. gambar rangkaian

5.Video[kembali]

6.Dwonload[kembali]

video klik disini

html klik disini

simulasi klik disini

data sheet transistor klik disini

data sheet battrai klik disini