1.Tujuan[kembali]

- Untuk menyelesaikan tugas sistem digital yg diberi oleh bapak Darwison,M.t

- untuk memahami materi sub-chapter 7.2 pada buku digital electronics_principles devices and applications dan contoh soal 7.6 pada buku Teori, rancangan dan aplikasi sistem digital

2.Alat dan Bahan[kembali]

Alat:

-ALAT

logicprobe

Logic probe atau logic tester adalah alat yang biasa digunakan untuk menganalisa dan mengecek status logika (High atau Low) yang keluar dari rangkaian digital. Objek yang diukur oleh logic probe ini adalah tegangan oleh karena itu biasanya rangkaian logic probe harus menggunakan tegangan luar (bukan dari rangkaian logika yang ingin diukur) seperti baterai. Alat ini biasa digunakan pada IC TTL ataupun CMOS (Complementary metal-oxide semiconductor).

Logic probe menggunakan dua lampu indikator led yang berbeda warna untuk membedakan keluaran High atau Low. Yang umum dipakai yaitu LED warna merah untuk menandakan output berlogika HIGH (1) dan warna hijau untuk menandakan output berlogika LOW(0).

BAHAN

Gerbang NAND

spesifikasi

konfigurasi pin

3.1 contoh soal[kembali]

1. Untuk rangkaian setengah penambah pada Gambar 7.23(a), input yang diterapkan pada A dan B adalah seperti yang ditunjukkan pada Gambar 7.23(b). Plot output SUM dan CARRY yang sesuai pada skala yang sama.

Jawab:

Bentuk gelombang SUM dan CARRY dapat diplot dari pengetahuan kita tentang tabel kebenaran penjumlah setengah. Yang perlu kita ingat untuk menyelesaikan masalah ini adalah 0+0 menghasilkan '0' sebagai output SUM dan '0' sebagai CARRY. 0 +1 atau 1+0 menghasilkan '1' sebagai output SUM dan '0' sebagai CARRY. 1 +1 menghasilkan '0' sebagai output SUM dan '1' sebagai CARRY. Bentuk gelombang keluaran adalah seperti yang ditunjukkan pada

Gambar 7.24.

2.Mengingat ekspresi Boolean yang relevan untuk rangkaian setengah-penambah dan setengah-pengurang, rancang rangkaian setengah-penambah-pengurang yang dapat digunakan untuk melakukan penjumlahan atau pengurangan pada dua bit satu.angka. Operasi aritmatika yang diinginkan harus dapat dipilih dari input kontrol.

jawab:

Ekspresi Boolean untuk setengah-penambah dan setengah-pengurang diberikan sebagai berikut:

Jika kita menggunakan inverter terkontrol untuk melengkapi A dalam kasus rangkaian setengah-pengurang, maka perangkat keras yang sama juga dapat digunakan untuk menambahkan dua angka satu bit. Gambar 7.25 menunjukkan rangkaian logika diagram.

Ketika input kontrol adalah '0', variabel input A dilewatkan tanpa pelengkap ke input dari gerbang NAND. Dalam hal ini, gerbang AND menghasilkan keluaran CARRY dari operasi penjumlahan. Itu Gerbang EX-OR menghasilkan keluaran SUM. Di sisi lain, ketika input kontrol adalah '1', AND gerbang menghasilkan keluaran BORROW dan gerbang EX-OR menghasilkan keluaran PERBEDAAN. Dengan demikian, '0' pada input kontrol menjadikannya setengah penambah, sedangkan '1' pada input kontrol menjadikannya setengah-pengurang.

3.2 problem [kembali]

Soal 7.6: Buatlah diagram blok, rangkaian dalam dan table kebenaran

dari IC 74138 Decoder

jawab:

diagram blok

2. Berikut sebuah untai logika yang dibentuk dari gerbang AND dan OR.

Untuk dapat merealisasikan untai tersebut, dibutuhkan 2 buah IC digital. Pertama, IC yang mempunyai gerbang AND yaitu 7408. Kedua, IC yang mempunyai gerbang OR yaitu 7432. Gerbang pertama dan kedua menggunakan dua buah gerbang pada IC 7408, dan gerbang ketiga hanya menggunakan sebuah gerbang pada IC 7432. Dengan memanfaatkan sifat universal dari gerbang NAND, ubahlah untai di atas agar dapat direalisasikan menggunakan gerbang NAND saja! Berapa IC yang dibutuhkan ?

Jawab :

Berdasar universalitas gerbang NAND dan NOR, gerbang AND dapat diwakili oleh dua buah gerbang NAND; sedangkan gerbang OR dapat diwakili oleh tiga buah gerbang NAND. Sehingga terbentuk 7 buah gerbang NAND seperti pada Gambar dibawahKita misalkan gerbang AND bagian atas diberi nomor 1 dan yang bawah diberi nomor 2, sedangkan gerbang OR di sebelah kanan diberi nomor 3. Gerbang nomor 1 dapat diganti dengan NAND menjadi gerbang nomor 1A dan 1B. Demikian pula gerbang nomor 2 dapat diganti menjadi gerbang nomor 2A dan 2B. Sedangkan gerbang nomor 3 yaitu OR dapat diganti dengan tiga gerbang NAND menjadi gerbang nomor 3A, 3B dan 3C. Terdapat dua pasang NOT ganda, yaitu gerbang 1B-3A dan 2B-3B. Kedua pasang NOT tersebut dapat dihilangkan. Sehingga hasil akhir hanya dibentuk oleh tiga buah gerbang NAND. Untai hasil hanya menggunakan tiga gerbang NAND. Karena sebuah IC NAND 7400 mempunyai empat gerbang NAND, maka realisasi untai tersebut hanya membutuhkan sebuah IC.

3.3 pilihan ganda[kembali]

1 Pada gambar diatas merupakan rangkaina logika kombinasional ...

a. Decoder

b. Encoder

c. Multiplexer

d. Demultiplexer

e. Adder

Pada gambar diatas merupakan rangkaian logika kombinasional ...

a. Decoder

b. Encoder

c. Multipelxer

d. Demultiplexer

e. Adder

4.Percobaan[kembali]

1.prosedur percobaan

- Siapkan semua alat dan bahan yang diperlukan

- Disarankan agar membaca datasheet setiap komponen

- Cari komponen yang diperlukan

- Coba dijalankan rangkaian

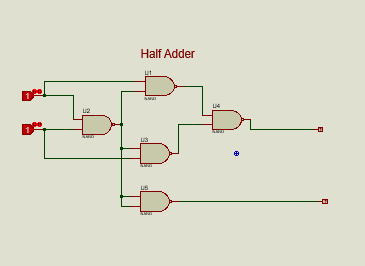

2. gambar rangkaian

3.prinsip kerja

Pada saat logic staate diberi logika 0, maka input pada U2 akan berlogika 0 dan mengeluarkan ouput berlogika 1. Lalu pada U1, U3, U5 terdapat input brlogika 0 dan 1 dikarenakan dari hasil U2 dan juga dari logic state. Pada U5 mengeluarkan output berlogika 0. pada U1 dan U3 berlogika 1. Lalu masuk ke U4 maka inputannya menjadi berlogika 1. dan U4 mengeluarkan output berlogika 0. Maka hasil akhirnya berlogika 0 dan 0 sesuai dengan tabel kebenaran Half Adder.

5.Video[kembali]

6.Dwonload[kembali]

video klik disini

simulasi rangkaian klik disini

data sheet gerbang nand klik disini

html klik disini